# Architecture and Interconnect Technologies for a Novel Conformal Active Phased Array Radar Module

Marc Schreiner ♦, Helmut Leier ♦, Wolfgang Menzel ♠, Heinz-Peter Feldle ♠

♦ DaimlerChrysler Research and Technology, 89081 Ulm, Germany; ♠ EADS, 89071 Ulm, Germany

♠ University of Ulm – Department of Microwave Techniques, 89081 Ulm, Germany;

**Abstract** — Highly integrated transmit / receive modules are key components for modern active phased array radar systems. This paper describes architecture and related interconnect technologies for a novel transmit / receive module with integrated radiating element and circulator for X-band applications. It allows the realization of future planar or conformal active antenna arrays with low installation depth as well as high maintainability performance.

## I. INTRODUCTION

Current developments in airborne radar technology deal with additional features such as sidelooking radar systems or active apertures integrated in the aircraft's surface.

An active phased array consists of tens to several thousands of T/R-modules. The cross section of the modules depends on the system requirements (e.g. max. operational frequency, max. scan angle) Novel curved antenna apertures additionally require smallest depth of the modules. Therefore, the challenge is the realization of highly integrated modules.

## II. NEW ARCHITECTURE FOR ACTIVE PHASED ARRAY SYSTEMS

In most known active phased array systems, the T/R-modules are mounted on the backside of the manifold separated from the radiating elements installed on the opposite side of the manifold [1-5]. The modules in this type of arrangement are only accessible from the backside of the radar system, which is a major drawback in terms of maintainability performance, especially if the system is to be deployed in a hardly accessible position such as an aircraft's wing. Furthermore this results in a quite complex manifold structure requiring additional vertical RF-feedthroughs traversing the manifold in order to connect the radiating element to the T/R-module.

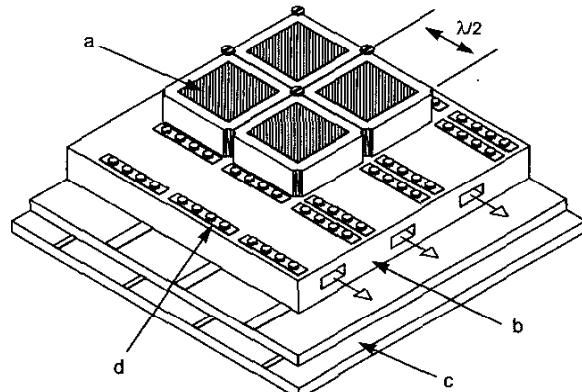

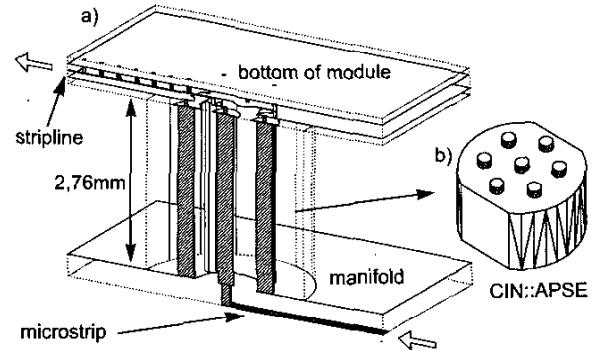

Fig. 1 illustrates a new approach. By combining the T/R-module, the circulator and the radiating element in one RF-frontend, it is possible to mount this frontend from the readily accessible side of the manifold. The manifold has a vertically stacked structure of several layers. The first layer (b in Fig. 1) is a cooling structure using liquid coolant, in case high output power is required. For low power applications a simple metal plate might be used for heat dissipation

Fig. 1 Basic system configuration: T/R-module with integrated circulator and radiating element (a), cooling structure (b), manifold (c), vertical interconnection structure (d)

instead. The multilayer manifold carrying the power supply, RF and digital signals is arranged behind the cooling structure. A vertical feedthrough based on coaxial push contacts (d in Fig. 1) traversing the cooling structure vertically provides the electrical interconnections between the manifold and the frontend.

The advantages of this kind of system architecture are the optimum overall performance of the module and its high maintainability performance. In case of service, no other parts but the array's radome have to be demounted in order to replace a frontend. Moreover the concept lends itself to adopting active phased arrays conformally to slightly bent structures such as an aircraft's wing due to its low installation depth.

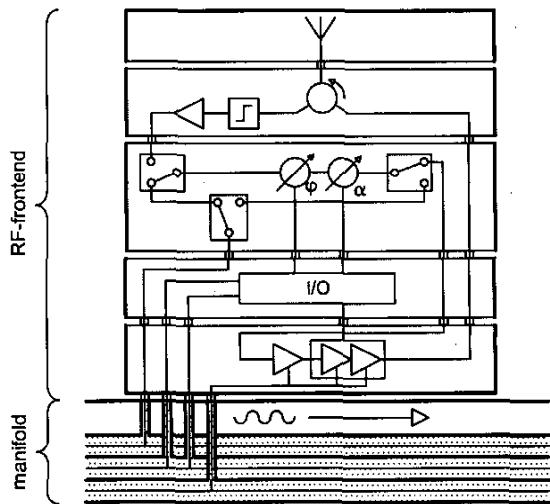

Fig. 2 shows an RF-frontend architecture that constitutes a good trade-off between optimized RF and thermal properties. All components included in the module are arranged in a vertically stacked manner in order to achieve a high degree of integration. The power amplifier and the driver amplifier are placed in the lowest layer to ensure high thermal conductance between the cooling structure and the amplifiers. The digital control unit having many connections to other devices is arranged centrally. Finally the low noise amplifier is located in close proximity to the antenna to reduce the module's noise figure.

### III. TECHNOLOGICAL CONCEPT FOR THE RF-FRONTEND

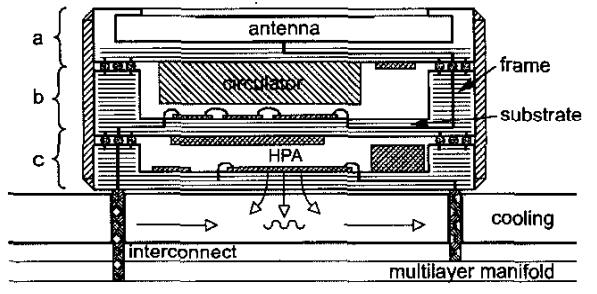

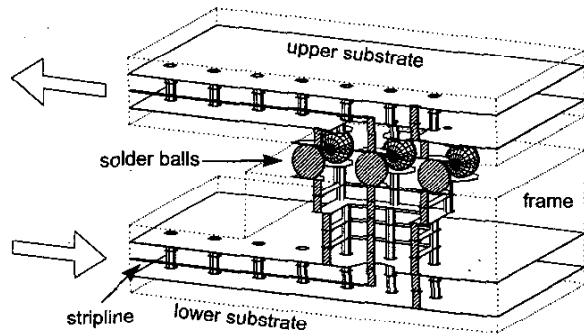

A concept for a possible realization of an RF-frontend according to the given frontend architecture is shown in Fig. 3. Three ceramic multilayer substrates with integrated frame structures are stacked vertically and interconnected by means of solder balls. Together with vias embedded in the frame structure the solder balls establish the interconnection for all signals between the substrates.

All components of the frontend, i.e. MMICs, ASICs, capacitors, resistors and the circulator are mounted in cavities which are formed by the integrated framestructure of the stacked substrates. The top cavity is used to build up the integrated cavity backed broadband patch element. All chips are attached by means of gluing or soldering and wire-bonding technology which keeps the production process compatible with common manufacturing facilities. To ensure a high level of integration and to keep the number of solder ball interconnects and layers as low as possible, the devices are partly mounted on both sides of the substrates. Finally a thin metal sleeve is brazed on the frontend's sidewalls to ensure hermeticity and to provide electric shielding between adjacent frontends deployed in an array.

The electrical interface of the module consists of flat gold-plated face-down contact pads (s. Fig. 7). The push interconnectors assembled into the manifold establish the electrical interconnect between the frontend's contact pads and the manifold's conductor tracks.

The frontends are fastened to the manifold by means of screws having their contact point at the edges of the frontend (s. Fig. 1). The screws generate the necessary compression force for the employed push interconnects and the thermal interface. The thermal interface is made of polymeric foil sandwiched between the module and the manifold. All substrates consist of aluminum nitride HTCC with a high thermal conductivity of  $150\text{ W}/(\text{m}\cdot\text{K})$ . This configuration features good thermal conductivity and spreads dissipated heat efficiently.

### IV. THREE-DIMENSIONAL RF-INTERCONNECT TECHNOLOGY FOR STACK-PACKED INTEGRATED MODULES

The AlN HTCC substrates employed in the frontend consist of four ceramic layers plus additional layers forming the frame structure. This configuration allows to have microstrip lines face-up and face-down as well as shielded stripline in the middle of the substrate offering sufficient flexibility for RF-signal routing. Each layer has a thickness of  $200\text{ }\mu\text{m}$ , the dielectric constant is  $\epsilon_r = 8.6$ . The face-up and face-down metallization is made of tungsten, nickel and gold, whereas the vias and the inside metalization are made of tungsten only, since the high sintering temperature of the HTCC ceramics doesn't permit the usage of metals with

Fig. 2 RF-frontend and manifold architecture.

Fig. 3 Physical realization: (a) circulator radiator assembly, (b) RF unit and digital control unit, (c) power amplifier

better conductivity such as gold or copper. In the following, different RF-interconnect structures which are essential for the design of highly integrated frontends are evaluated.

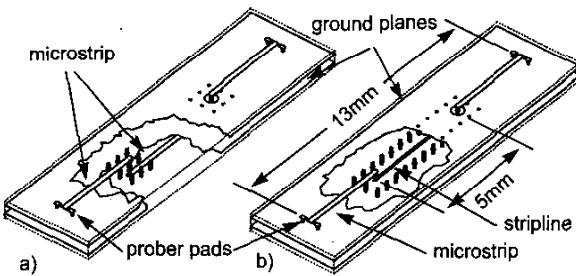

#### A. RF-interconnections within one substrate

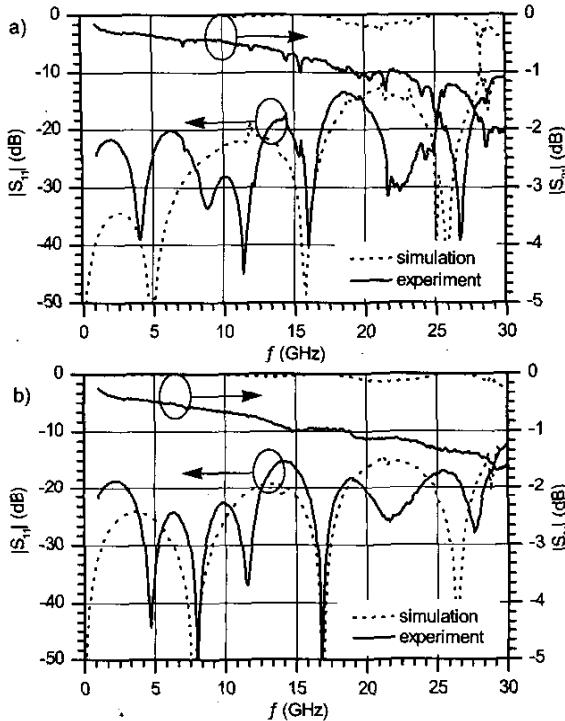

Fig. 4a shows a microstrip face-up to microstrip face-down structure with a quasi-coaxial feedthrough and Fig. 4b shows a microstrip to stripline transition with a via shielding structure preventing the propagation of parallel plate modes [6-8]. Both structures were optimized with FEM and FDTD fullwave simulations. Fig. 5 displays the respective measurements and simulation data (these do not include ohmic and dielectric losses). In X-band, the structures are well matched, insertion losses are predominantly due to ohmic losses, especially in the tungsten stripline.

These structures are suitable to establish RF-connections between components mounted on the top and bottom of the substrate or to underpass other components with RF-lines.

Fig. 4 (a) microstrip face-up to microstrip face-down transition (b) microstrip to stripline transition.

Fig. 5 Simulated and measured s-parameters of a microstrip (face-up) to microstrip (face-down) transition (a) and microstrip to stripline transition (b).

#### B. RF-interconnects between two substrates

Since all layers of the frontend include RF-components, efficient RF-interconnects between the vertically stacked substrates are required. Important properties of the interconnects are low insertion loss, sufficient shielding, high mechanical stability, compactness, compatibility to the multilayer structures and easy assembly, respectively.

These requirements can be met with the solder ball interconnection shown in Fig. 6. Nine solder balls form a coaxial structure. The RF-conducting solder ball is connected to the striplines in the multilayer substrate by means of vias. Rows of grounded vias connected to the other solder ball provide the ground connection and ensure shielding. The

Fig. 6 RF solder ball interconnect between two substrates with stripline terminals (split in the H-symmetry plane)

matching can be improved by including a taper structure for the grounded vias within the frame. The solder ball have a diameter of  $500\mu\text{m}$  and are arranged in a grid with  $800\mu\text{m}$  spacing. The structure was optimized by EM-simulation using FEM method.

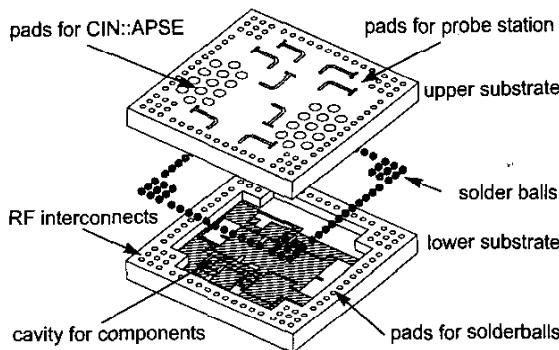

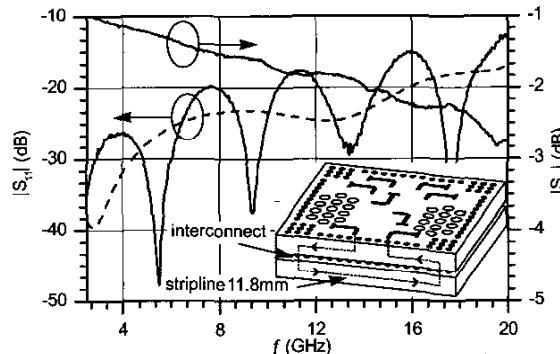

In order to check the performance of the interconnect, a test vehicle (Fig. 7) was built up. The substrate used is equivalent to the substrates that will be used for the complete frontend in terms of size, material and shape. It comprises structures for a double solder ball interconnect and TRL calibration structures. The measured insertion loss at 10 GHz was  $-1.65\text{ dB}$  for the whole structure (Fig. 8). The losses are largely due to the  $11.8\text{ mm}$  long stripline (measured insertion loss:  $\alpha = 0.085\text{ dB/mm}$ ) between the two interconnects. The dashed line in Fig. 8 is showing the return loss of one interconnect that was extracted by time domain measurement and windowing.

Extensive reliability tests were performed with the solder ball interconnect using thermal cycling (2000 cycles,  $\Delta T = 200\text{ }^\circ\text{C}$ ) and pressure cooker tests (1000h at 2.5 bar), without any failure of degradation in performance. Details on this will be presented elsewhere.

#### C. RF-interconnect between frontend and manifold

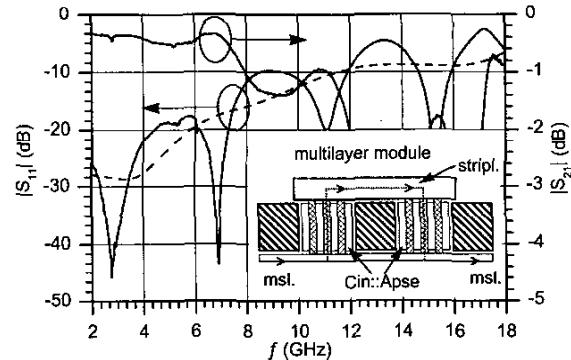

Finally a suitable interconnect between frontend and manifold is needed. It has to be easily detachable, compact, and it has to compensate for thermal stress. An appropriate solution meeting these requirements are flexible cylindrical contacts made of fine wire mesh embedded in an dielectric spacer, e.g. CIN::APSE of FuzzButton [1]. This technology can be used for power and data signals as well as for all RF signals up to X-band [1],[9].

A coaxial CIN::APSE interconnect between a multilayer stripline with contact pads on the bottom of the module and a microstrip line being part of an experimental manifold is shown in Fig. 9a, the measured S-parameters of a double CIN::APSE interconnect are shown in Fig. 10. Return loss at 10GHz is below  $-12\text{ dB}$ , insertion loss is approx.  $0.35\text{ dB}$ .

Fig. 7 Test vehicle for evaluation of 3D-interconnect technology between vertically stacked AlN HTCC substrates.

Fig. 8 Measured S-parameters of a double solder ball interconnect (—) and a single solder ball interconnect (---).

## V. CONCLUSION

A new architecture for a highly integrated frontend (patent pending) for X-band applications has been presented and appropriate RF-interconnect structures and packaging technologies were demonstrated. As a result, a complete frontend demonstrator will be built up and tested in terms of RF-performance and reliability. Preliminary results will also be available at the conference.

## REFERENCES

- [1] M. S. Hauhe, J. J. Wooldridge, "High density packaging of X-band active array modules", *IEEE Transactions on Components, Packaging, and Manufacturing Technology, part B: Advanced Packaging*, vol. 20, no. 3, pp. 279-291, Aug. 1997

- [2] J. A. Reddick III, R. K. Peterson, M. Lang, W. R. Kitzler, P. Piacente, W. P. Komrumpf, "High density microwave packaging program phase 1-Texas Instruments/Martin Marietta team", *1995 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, pp. 173-176, June 1995

- [3] J. A. Costello, M. Kline, F. Kuss, W. Marsh, R. Kam, B. Fasano, M. Berry, N. Koopman, "The Westinghouse high density microwave packaging program", *1995 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, pp. 177-180, June 1995

- [4] D. Strack, G. Ferrell, A. Piloto, J. Gipprich, J. Fisher, J. Kennedy, D. Heffernan, S. Caswell, "Low cost T/R modules for planar arrays", *1997 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, pp. 579-582, June 1997

- [5] R. Sturdvant, Ly Chung, J. Benson, M. Hauhe, "Design and performance of a high density 3D microwave module", *1997 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, pp. 501-504, June 1997

- [6] W. Menzel, J. Kassner, "Millimeter-wave 3D integration techniques using LTCC and related multilayer circuits" *2000 European Microwave Conference, Digest* vol. 2, pp. 33-36, October 2000

- [7] E. R. Pillai, "Coax via-A technique to reduce crosstalk and enhance impedance match at vias in high-frequency multilayer packages verified by FDTD and MoM modeling", *IEEE Trans. Microwave Theory and Tech.*, vol. 45, no. 10, pp. 1981-1985, October 1997

- [8] G. E. Ponchak, C. Donghoon, J.-G. Yook, L. P. B. Katehi, "The use of metal filled via holes for improving isolation in LTCC RF and wireless multichip packages", *IEEE Trans. on Packaging and Manufacturing Technology*, vol. 23, no. 1, pp. 88-99, February 2000

- [9] E. Saint-Etienne, B. Reig, F. Deborgies, J.-P. Ghesquiers, D. Roques, G. Le Meur, B. Cogo, Y. Mancuso, "Silicon packing and RF solder-free interconnect for X-band SAR T/R module", *GAASC 2001, The European Gallium Arsenide and related III-V Compounds Application Symposium*, pp. 231-234

Fig. 9 (a) CIN:APSE interconnect between manifold and module split in the H-symmetry plane, (b) CIN:APSE interconnector

Fig. 10 Measured S-parameters of a double CIN:APSE interconnect (—) and a single CIN:APSE interconnect (---).